近日,有媒体指出成功登陆火星的美国太空总署(NASA)毅力号所使用的是20 多年前技术的处理器。对此,许多网友展开了关于“为什么航空航天处理器如此落后”、“航天器中的宇航级芯片设计有什么特别之处?”之类的讨论。

EDN在本文就与读者一起看看,为何毅力号火星车CPU采用的98年的架构,主频才233MHz,却要20万美金一颗!

为何毅力号选用20多年前技术的处理器?

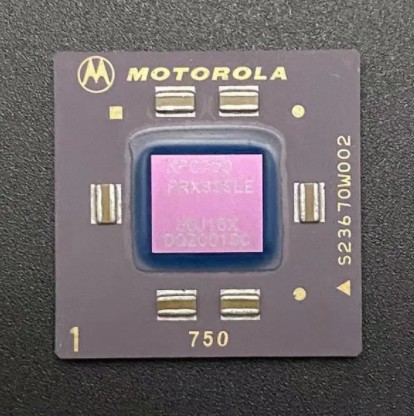

据了解,毅力号火星探测器搭载的机智号火星直升机,它使用的是民用、消费级芯片组高通骁龙 801处理器。这款处理器发布时间是2014年,与当前高通骁龙888处理器相比已经非常落后。然而毅力号使用的更是1998年生产的PowerPC 750处理器,那为什么毅力号会选用20多年前技术的处理器呢?

外媒报道,毅力号搭载的处理器型号为PowerPC 750 处理器,与1998年苹果出品的iMac G3 电脑同款,对比苹果最近推出的M1 ARM 架构处理器拥有最高主频3.2GHz,晶体管数量达160 亿个,PowerPC 750 处理器最高主频速度仅233MHz,且晶体管数量也只有600 万个,但单价仍高达20 万美元(约130万元)。

报道解释,毅力号的PowerPC 750 处理器单价会如此昂贵,并非因为性能超强大,而是必须应对未知的太空环境,因此对处理器进行抗辐射、耐寒冷功能等强化,美国航空航天局花费20万美元由BAE系统公司进行定制生产 。此处理器虽然架构依旧,但结构强化与优化,导致价格昂贵,也非量产型处理器。它是由BAE Systems使用0.25或0.15um工艺制造的,管芯面积为130mm²。CPU本身可以承受200,000至1,000,000 Rads,温度范围为−55至125°C。

报道进一步指出,NASA 之所以选择旧架构处理器的原因,在于旧架构处理器运作可靠度更成熟。因毅力号火星探测器较特殊,需要长时间稳定运行,因此执行主频速度成其次,且毅力号一般运作并不需要太强大的运算能力。故就需求来说,旧架构PowerPC 750 处理器完全可以胜任。

而机智号火星直升机使用的骁龙处理器成本相对来说比较低,因为该直升机只会进行简单的任务不参与重要任务。再加上保暖系统后机智号可以让处理器保持在特定的温度中,这样不必花费太多钱进行定制又不至于太容易损坏。

航天器中的宇航级芯片设计有什么特别之处?

宇航级芯片是航天航空电子装备的心脏,宇航级芯片必须具备抗辐照特性,其身价往往是我们生活中常见的消费级芯片的数十倍,甚至成百上千倍。那么,与消费级芯片相比,这些昂贵的宇航级芯片在设计阶段有什么特别之处呢?知乎用户@Forever snow 作出了详细的解答。

1.宇航级芯片所处的空间环境

在航天器运行的空间环境中,存在着大量的高能粒子和宇宙射线。这些粒子和射线会穿透航天器屏蔽层,与元器件的材料相互作用产生辐射效应,引起器件性能退化或功能异常,影响航天器的在轨安全。引起器件辐射效应的主要空间辐射源包括地球辐射带、银河宇宙射线、太阳宇宙线和人工辐射。

其中,对芯片工作影响最为严重的辐射效应当属“单粒子效应”。

据数据统计,从 1971 年到 1986 年间,国外发射的 39 颗同步卫星共发生了 1589 次故障,有 1129 次故障与空间辐射有关,且其中的 621 次故障是由于单粒子效应导致的。这些统计数据说明了航天应用中电子器件的主要故障来自于空间辐射,而单粒子效应导致的故障在其中占较大比重。

这些故障中,部分是永久性不可逆的,如发生单粒子锁定导致芯片内部局部短路从而产生大电流烧毁器件。针对此类错误可以应用一些特定工艺或器件库来避免。而太空中大部分错误是由于半导体器件的逻辑状态跳变而导致的可恢复的错误,如单粒子翻转导致存储器存储内容错误。

单粒子翻转(Single-Event Upsets,SEU)指的是元器件受辐照影响引起电位状态的跳变,“0”变成“1”,或者“1”变成“0”,但一般不会造成器件的物理性损伤。正因为“单粒子翻转”频繁出现,因此在芯片设计阶段需要重点关注。这也是这篇文章的重点。

2.在芯片设计阶段如何防护“单粒子翻转”

(1) 选择合适的工艺制程

在航天领域,并不是工艺制程越小越好。通常来讲,工艺制程越小,抗辐照能力越差。因此,为了确保可靠性,一般会选择较大线宽的制程,比如0.18um、90nm、65nm等,而不会一味追求摩尔定律的前沿制程。

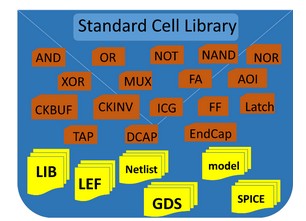

(2)加固标准单元工艺库

标准单元工艺库是数字芯片的基石。如果把数字芯片看做一个建筑,标准单元工艺库就是构成建筑的砖块。标准单元工艺库包括反相器、与门、寄存器、选择器、全加器等多种基本单元,每一个标准单元对应着多个不同尺寸(W/L)、不同驱动能力的单元电路,基于这些基本单元即可构成复杂的数字芯片。

鉴于数字芯片的超大规模,已经很难通过全定制电路结构的方式来设计,而直接对商用工艺库进行加固则是设计成本最低的选择。在制造厂商提供的标准单元库基础上结合抗辐照加固措施,使设计出来的输入输出单元库具有抗辐照能力。加固之后的工艺库需要晶圆厂流片验证。

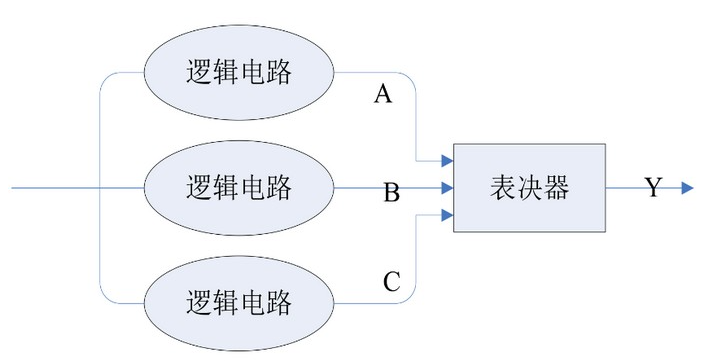

(3)设计冗余化

在抗辐照加固方法中,三模冗余(TMR)是最具有代表的容错机制。同一时间三个功能相同的模块分别执行一样的操作,鉴于单粒子翻转瞬时仅能打翻1路,“三选二”的投票器将会选出其余两路的正确结果,增强电路系统的可靠性。三模冗余最显著优点是纠错能力强,且设计简单,大大提高电路可靠性;但缺点也是显而易见,会将电路增大3倍以上。TMR的方法较为灵活,可根据性能需求在寄存器级、电路级、模块级等任意层次设计TMR,部分EDA工具也可自动插入。

错误检测与纠正电路(Error Detection And Correction,EDAC)也是一种简单高效的防护单粒子翻转的电路设计方法。EDAC 主要依据检错、纠错的原理,通过转换电路将写入的数据生成校验码并保存,当读出时靠对校验码进行判定,若只有一位出错系统则自动纠正并将正确的数据输出,同时还会进行数据的回写从而覆盖原来出错的数据。EDAC尽管纠错能力强大,但是需要纠错、译码电路,因此结构较为复杂,不适宜用于高性能的数据通道中。EDAC也可用于纠正多bit出错的情况,但是纠错电路会更加复杂。

权衡TMR和EDAC的优缺点,通常会在逻辑电路设计中使用TMR,在存储器读写电路中使用EDAC。

(4)模块独立化

单粒子翻转频繁出现,必须考虑到翻转发生之后不影响芯片的整体功能。因此,在架构设计中需要尽可能确保模块之间保持较强的独立性,尽可能具备独立的复位功能,使得在单粒子打翻信号值之后,一方面出错电路能够尽快通过复位信号恢复正常;另一方面,确保其他正常工作的模块不受影响。此外,还需增加异常检测电路,发现异常即可对电路进行复位。

虽然上述方法可以很好地防护单粒子翻转效应,但是也给逻辑综合、布局布线带来很多困扰,在芯片物理实现过程中需要小心谨慎应对。除上述方法外,还可引入Muller C单元、双互锁存储单元结构(DICE)对晶体管级电路进行防护,也可在版图阶段使用环形栅替换条形栅。

小结

在航天领域中,芯片的性能并不是第一考虑要素,可靠性才是重中之重。只有芯片具备抗辐照能力,才能确保航天器正常运行。