大型重离子对撞机实验(ALICE)是大型强子对撞机(LHC)上唯一致力于研究极端相对论下的原子核碰撞的实验。其目标是研究强相互作用物质在实验室达到的极高能量密度下的物理特性。在极高能量密度下,能够产生一种新的物质形态——夸克-胶子等离子体。宇宙被认为在大爆炸后的最初几百万分之一秒就处于夸克-胶子等离子体状态。在实验室里重现宇宙初期的物质形态并理解它是如何演化的,将有助于理解当今物质世界的形成和组分以及夸克和胶子的禁闭机制等物理学前沿重大科学问题。为此,ALICE 对重核(如铅核)碰撞产生的强子、电子、缪子和光子进行了全面的探测和研究。为了与核-核碰撞相比较,ALICE 也研究质子-质子和质子-核碰撞。至2021 年,ALICE 将完成探测器的重大升级,以进一步增强其探测能力,并在未来十多年继续在LHC上进行它的科学探索之旅。

01 ALICE 探测器升级简介

ALICE今年将完成其探测器、数据采集和数据处理系统的升级,提高物理探测能力,从而提高夸克-胶子等离子体的特征的提取精度,并探索量子色动力学(QCD)中的新现象。

为了精确测量强相互作用物质,ALICE将专注于稀有探针,如重味粒子、夸克偶素、光子、低质量双轻子,以及喷注淬火和奇异核的研究。观测稀有现象需要非常大的数据样本。在LHC第三次运行期间,铅核-铅核反应率预计将达到五万赫兹,对应的瞬时亮度为6 × 1027 每平方厘米每秒。这将使ALICE 积累的积分亮度和数据样本比目前所获得的大十倍以上。此外,由于径迹探测器精度的提高,升级后的探测器系统对含有重味夸克的短寿命粒子的探测效率更高。

在LHC 第二次长停机期间(2019~2021 年),ALICE 要进行几项重大升级:一个新的高分辨率、低物质量的硅像素内寻迹系统(ITS2)和一个新的前向缪子径迹探测器(MFT),时间投影室的读出室升级为气体电子倍增(GEM)探测器并采用全新的快速读出装置,升级多个子探测器的读出电子学系统,新型快速相互作用触发(FIT)探测器,和集成的在线-离线计算系统,以处理和存储大量数据。

利用升级后的探测器,ALICE将实现如下物理目标:拓展对开粲、开底介子和重子的精确测量范围至横动量零,研究重夸克与夸克-胶子等离子体的相互作用,确定QGP的输运系数,研究粲夸克热化程度及其强子化。拓展对J/ψ,ψ ' 的精确测量至极低的横动量区,并实现对瞬生和非瞬生J/ψ的有效分离,以探索热密物质环境下粲偶素的离解和再产生,研究色禁闭解除和介质温度。为确定QGP的初始温度和状态方程等提供重要信息,测量低不变质量、低横动量区的双轻子产生,探寻手征对称性恢复的信号。通过测量喷注内强子组分、重味喷注的产额等,研究喷注淬火效应和热密物质环境对部分子碎裂的影响。测量轻核和超核的产生,研究它们的产生机制和参与集体运动的程度。

本文主要介绍ALICE内寻迹系统的升级:这是2011 年启动的一项重大国际合作研发工作。包括中国在内的15 个国家的35 个研究机构一起,经过为期五年的密集研发计划,于2017~2019 年完成探测器各关键部件的成功原型制作和生产,运抵欧洲核子研究中心(CERN)后在CERN 167 号楼进行组装和测试。建成的新的内寻迹系统于2021 年初安装在LHC隧道ALICE实验的洞穴里。

02 新的内寻迹系统

新的内寻迹系统(即ALICE第二代内寻迹系统——ITS2) 是一种基于互补金属氧化物半导体(CMOS)的单片有源像素传感器(MAPS)的全像素硅探测器,覆盖中心快度区(|η|<1.3)。在MAPS 技术中,用于电荷收集的传感器和用于数字化的读出电路都在同一块硅片中,而不是通过凸点连接在一起。ALICE 开发的芯片称为ALPIDE。使用该芯片,ITS2 每层材料的辐射厚度比第一代ITS 减少了7 倍。ALPIDE芯片的尺寸为15×30 平方毫米,包含50 多万像素。它的低功耗(<40 毫瓦每平方厘米)和当前国际上最出色的空间分辨率(<5 微米)非常适合ALICE的内层径迹探测。

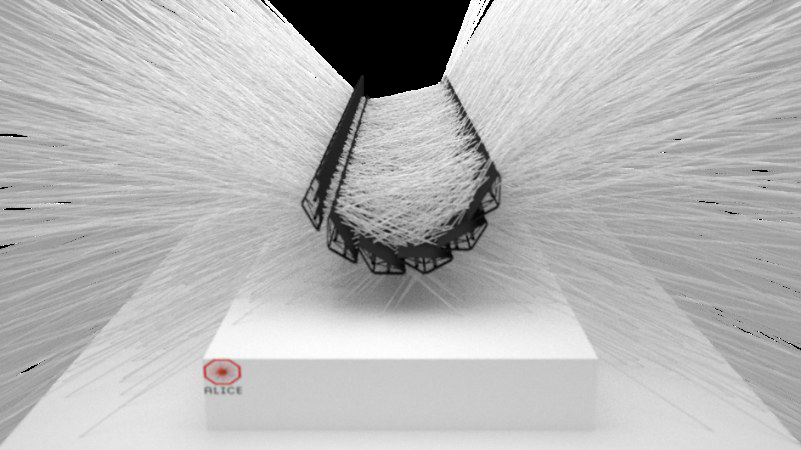

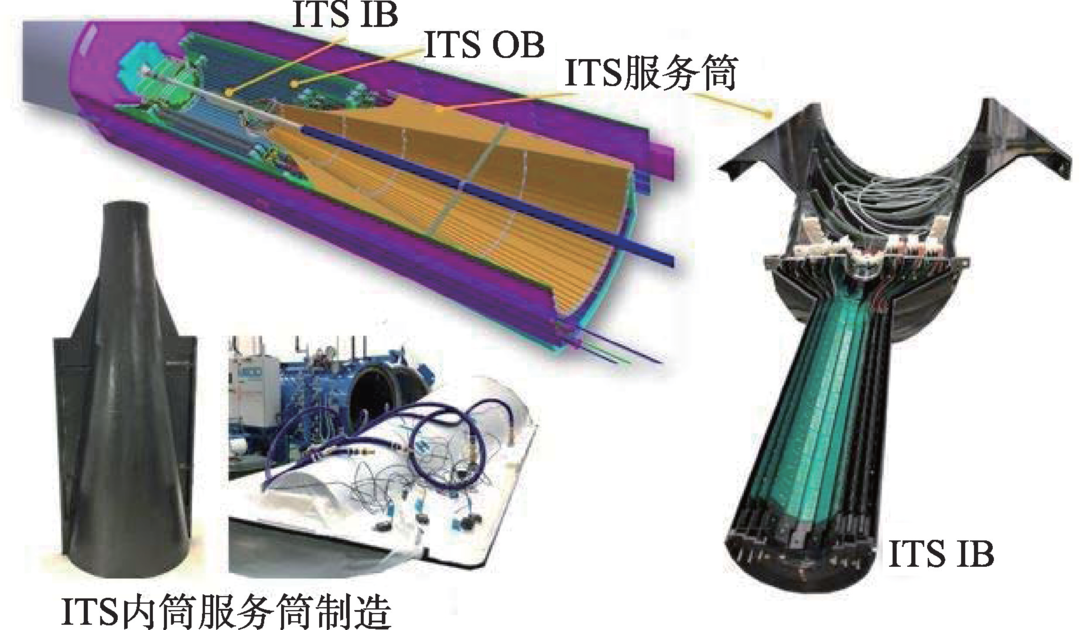

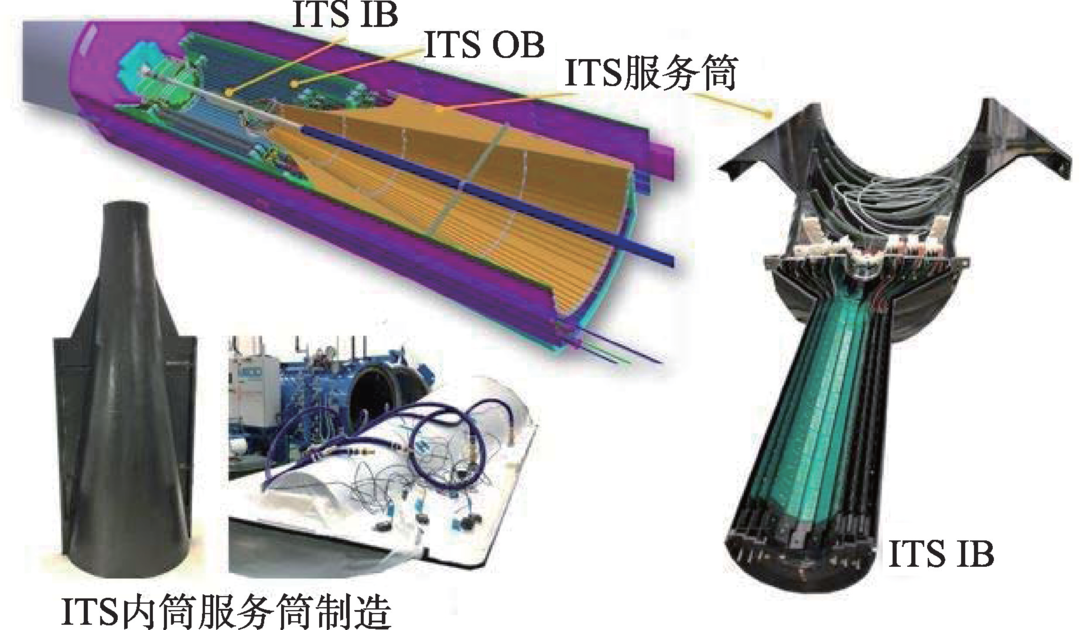

如图1 所示,ITS2 是由ALPIDE 芯片构成的七个圆柱形筒组成,分为两个子系统:内筒(IB)由27厘米长的三层组成,半径分别为2.3、3.1 和3.9 厘米;外筒(OB)由两个84 厘米长的中间层(ML)组成,半径分别为24 和30 厘米,两个148 厘米长的外层分别位于42 和48 厘米处。芯片总面积为10 平方米,含125 亿个像素单元。新设计的束流管半径为18.6 毫米(以前为39 毫米),允许ITS2 的最内层以22.4 毫米的半径靠近束流轴。

图1 新的ALICE ITS 设计以及内、外筒各层

图1 新的ALICE ITS 设计以及内、外筒各层

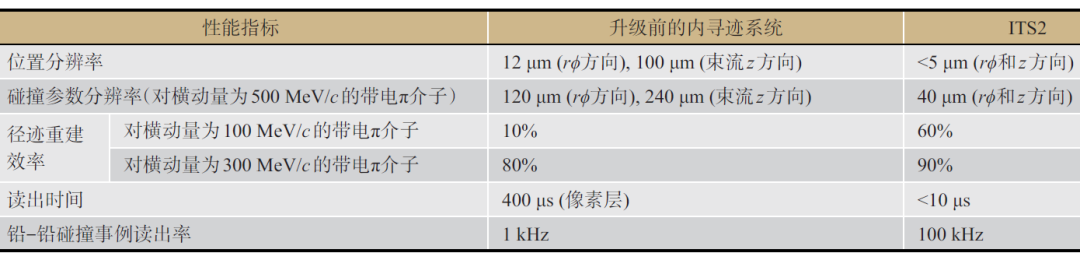

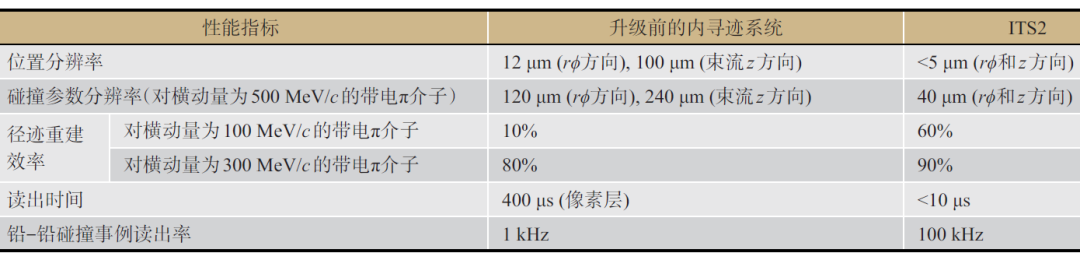

ITS2 将提高碰撞参数分辨率,横向平面(rϕ)提高三倍,束流轴(z)方向上提高五倍。它将把寻迹能力扩展到更低的横动量,使ALICE能够以前所未有的精度对重味强子进行测量。ITS2 还将增强读出能力,允许在超过五万赫兹的反应率下进行数据读出和记录。读出速度的提高以及新的数据采集系统的部署,将允许记录所有碰撞事例,若转化为可收集的最小偏差统计数据,比升级前的ALICE的数据采集能力提升了大约两个数量级。表1 给出了内寻迹系统升级前后的性能比较。

表1 内寻迹系统升级前后的性能比较

03 ALPIDE 芯片

ITS2 所期望的高水平的顶点重建和寻迹性能对探测器的粒度和材料的辐射厚度提出了严格的要求。为迎接这一挑战,包含中国组在内的ALICE-ITS2 芯片研发合作组联合开发了一款专用的MAPS芯片,即ALPIDE,将像素传感器和读出电子学器件集成在一起。

ALPIDE 芯片的大小为15×30 平方毫米,采用Tower 半导体公司提供的180 纳米CMOS工艺。该工艺的一个关键特征是深p-阱层(深p-型植入物),如图2,将包含PMOS晶体管的n-阱(n-阱植入物)从外延层屏蔽并且防止它们收集信号电荷,从而允许在像素电路中实现完整的CMOS(N 型金属氧化物半导体NMOS和P 型金属氧化物半导体PMOS)电路,并使ALPIDE 成为第一个具有类似于混合像素探测器的稀疏读出的CMOS 芯片。总电离剂量(TID)容限要求是用小厚度栅氧化层实现的,而电阻率大于1000 欧姆厘米的25 微米p 型外延层和对衬底施加反向偏压的可能性增加了对非电离能量损失(NIEL)的耐受性。束流测试表明,在TID 和NIEL 辐射后,在大的阈值范围下,ALPIDE 芯片具有良好的性能,探测效率大于99%,空间分辨率在5微米以下。

图2 ALPIDE芯片的CMOS像素传感器的截面示意图

图2 ALPIDE芯片的CMOS像素传感器的截面示意图

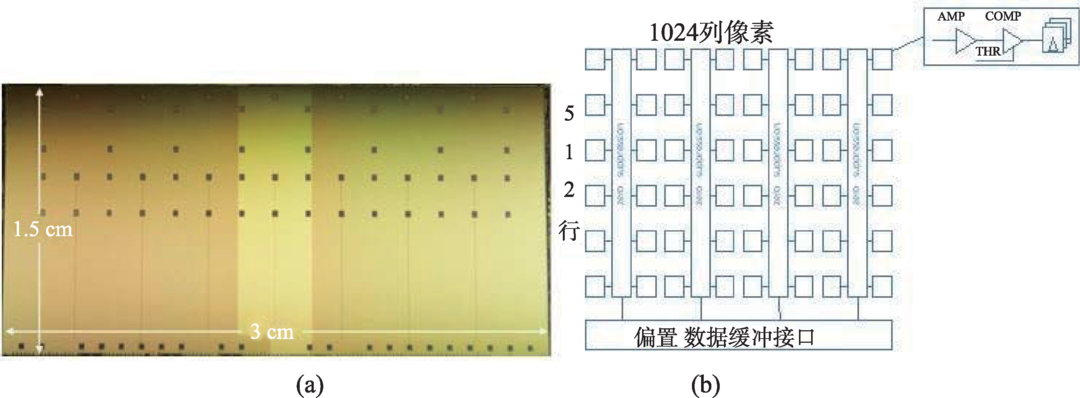

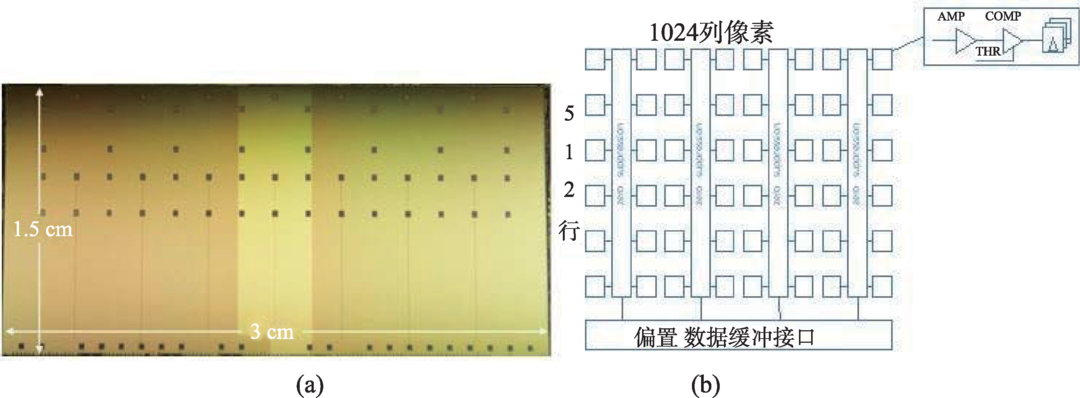

ALPIDE 芯片包括一个由29.24×26.88 平方微米的像素单元组成的512×1024 矩阵(图3),以及模拟偏置、控制、读出和接口。每个像素单元包含一个感测二极管、一个前端放大器和整形器、一个甄别器和一个数字电路部分。像素单元按双列排列,并由优先级编码器读出,该编码器将记录命中的像素的地址发送到芯片外围电路读出。没有击中的像素不被读出,使得读出过程更快,并且降低了功耗,每个像素的功耗约为40 纳瓦。信号感测二极管比像素单元小100 倍。穿过传感器的带电粒子通过电离释放材料中的自由载流子。在外延层中释放的电子向侧向扩散,而保持在纵向位置基本不变。当它们到达感测二极管的耗尽区(或直接在其耗尽区释放)时,耗尽区中的电场将它们扫向二极管触点。空穴由基板和p 型阱收集。由外延层中的载流子运动引起的二极管电流由像素前端读出。在衬底上施加适当的反向偏压可以增加收集二极管周围的耗尽区,提高信噪比。

图3 ALPIDE的图片(a)和读出结构(b)

图3 ALPIDE的图片(a)和读出结构(b)

04 探测器建造

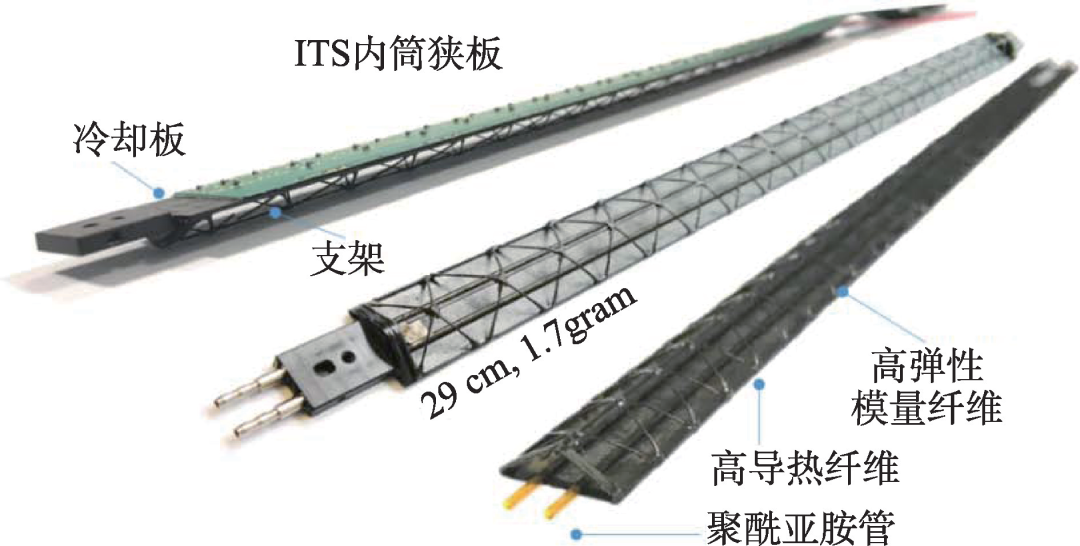

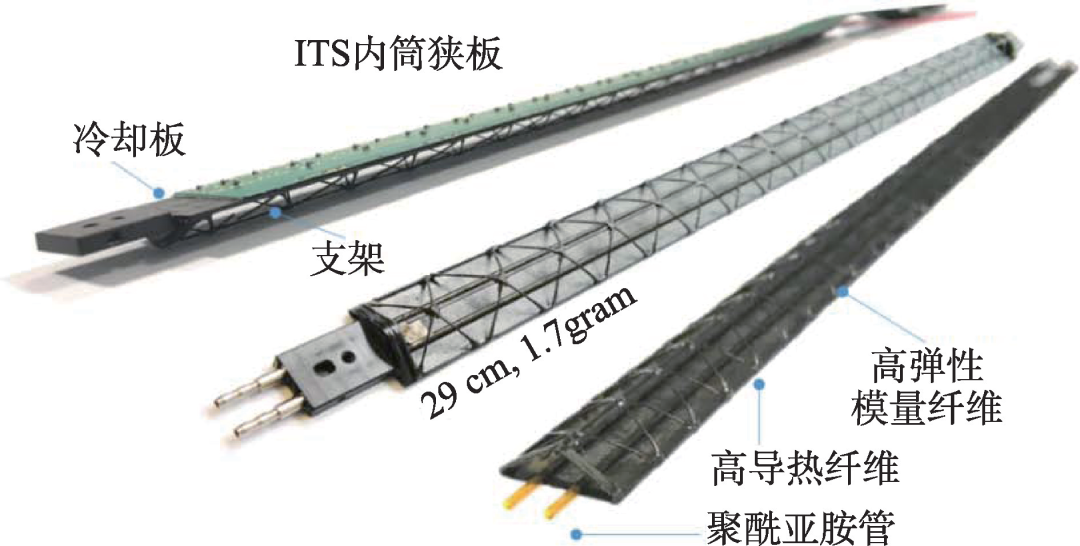

ITS 的升级对机械工程提出了挑战。ALPIDE传感器的结构支撑需要嵌入冷却系统,并要尽量减少材料的辐射厚度,以确保高性能。为此,ALICE开发出超轻高导热碳结构冷却板,板中嵌入能在亚大气压下工作的微型聚酰亚胺水冷管。

ALPIDE芯片散发的热量通过碳板进入冷却管道,最后通过管道中流动的水排出。聚酰亚胺管的直径非常小,小于1 毫米,ITS2 内三层的管壁厚度仅为25微米。

为确保机械稳定性,冷板由空间框架支撑,空间框架是一种具有三角形横截面的轻质丝缠绕碳结构。这一概念既适用于ITS2 内筒(IB)三层的狭板(如图4),也适用于外筒(OB)的四层狭板。每一层基于不同的几何和热约束来定制。每个IB 狭板(包括冷却管)的重量仅为1.7克。

图4 IB HIC模块粘在机械支架上组装成的IB 狭板

图4 IB HIC模块粘在机械支架上组装成的IB 狭板

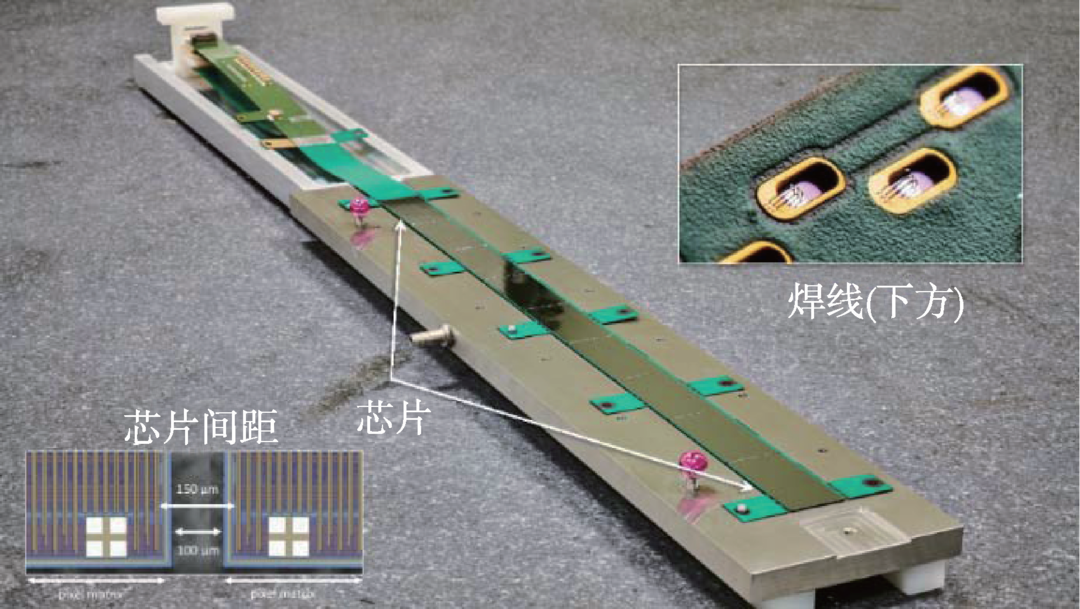

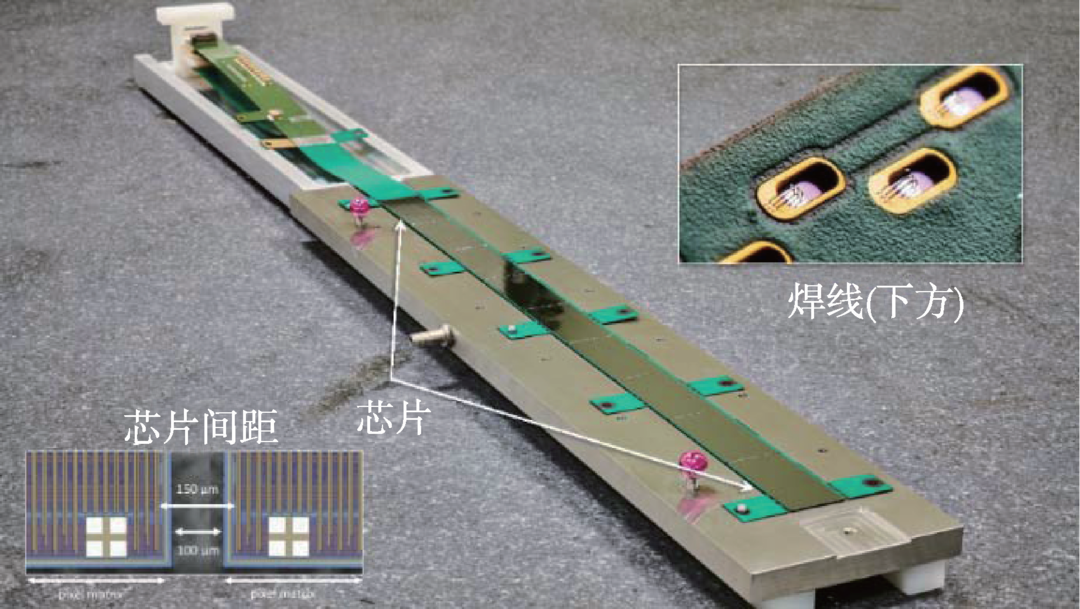

IB 狭板由一个IB 混合集成电路(HIC)模块组成。IB HIC 模块由九个厚50 微米的ALPIDE 芯片组成(见图5)。这些芯片在ALICE定制的模块组装机器ALICIA 中对齐,并粘贴在铝基柔性印刷电路(FPC)上。芯片焊盘通过导线绑定到FPC过孔。每个芯片分别以十二亿比特每秒的速度与其他芯片并行读出。最后,IB HIC被粘在一个冷板上。

图5 内层HIC模块的照片。插图显示了相邻芯片之间的间距以及通过导线连接到柔性印刷电路板的绑线

图5 内层HIC模块的照片。插图显示了相邻芯片之间的间距以及通过导线连接到柔性印刷电路板的绑线

OB狭板由两个半狭板组成。OB分为两个中间层和两个外层,它们具有相同的设计,但长度不同,中间层的半狭板由四个OB HIC模块组成,而外层由七个OB HIC 模块组成。OB HIC 由14 个厚100 微米的ALPIDE芯片组成,分为两行:每行的第一个芯片作为主芯片,在同一行的其他6 个芯片之间传输控制信号和数据。与时钟信号、控制信号和数据线相对应的芯片焊盘与铜基柔性线路板连接。对于OB,供电线是通过6 个铝卡普顿交叉电缆直接焊接到FPC上。

使用坐标测量机(CMM),将4 个(用于中间层)或7 个(用于外层)OB HIC 对齐,并粘在碳复合冷板上。HIC 通过在其短边上焊接导电桥而彼此互连。FPC 扩展被添加到第一个HIC 上,以将全链连接到外部读出和控制系统。这样就建造出OB半狭板。

将两个半狭板对齐并部分重叠地粘合到具有相应长度的空间框架上,形成完整的OB狭板。然后将半狭板的左右两侧延伸的交叉电缆焊接到一个铝卡普顿电源总线上。

狭板按半层组装,并插入结构筒壳中,如图6 所示为内筒,而图7 为外筒组装时拍摄的照片。三个内半层构成内筒的一半,而四个外半层构成外筒的一半。

图6 内筒的三个半层由24 个狭板组成。内筒将ITS2 的最内层固定在离束流管两毫米的位置

图6 内筒的三个半层由24 个狭板组成。内筒将ITS2 的最内层固定在离束流管两毫米的位置

图7 在欧洲核子研究中心167 号楼ITS 组装厅组装时拍摄的照片。其外筒上半部分的第5 层和第6 层(L5T和L6T)已经组装好,而第3 层(L3T)和第4层(L4T)正在组装中

图7 在欧洲核子研究中心167 号楼ITS 组装厅组装时拍摄的照片。其外筒上半部分的第5 层和第6 层(L5T和L6T)已经组装好,而第3 层(L3T)和第4层(L4T)正在组装中

ITS2 的桶部和整个机械装置的设计受到了新的探测器布局和新的安装要求的进一步挑战。服务设施只能在一侧连接,以便在每年冬季LHC停机期间能较快接近ITS2,而无需拆卸周围的探测器。

一种新的安装策略允许半个ITS2 探测器沿束流管平移约3 米。在平移过程中,两个半个ITS2 逐渐接近最终位置,最内层与束流管的径向距离仅为2毫米。

05 探测器预调试

所有机械结构于2018 年完工。第一批装备齐全的内筒狭板于2017 年完成生产,并在CERN 的SPS 重离子碰撞实验条件下进行了测试,而其他狭板的生产于2019 年底完成。所有其他主要探测器组件(读出电子设备、配电系统、触发器、数据采集、探测器控制)和运行保障设备(电源、冷却设备)也已生产并成功测试。

自2018 年5 月以来,合作组开始用宇宙射线测试不同的探测器组件。在CERN的167 号楼的一个特定区域内,值班人员控制探测器的各种参数,并收集数据。预测试取得了大量的试验结果,各子系统的运行参数及其整体性能得到了优化。此外,这些测试结果允许仔细检查任何遗留问题,并在2021年初安装到ALICE洞穴之前得到解决。

测试结果表明,探测器的热噪声极低,小于6 e,加上约20 e 的阈值偏差,探测器工作时的信噪比大于10,探测效率大于99%。探测器的各项性能均超出原设计指标要求。图8 所示为假命中率(在无束流的环境下以50 kHz读出率采集数据时,有信号输出(称为被击中)的像素计数除以总事例数和总像素数)随屏蔽掉的像素数的变化情况。在屏蔽掉2800万个像素中击中率较高的42 个像素后,第0 半层的假命中率下降到10-10/像素/事件以下。此外,测试结果证实了所采用的技术的可靠性,因为随着时间的推移,探测器的性能保持非常稳定。

图8 假命中率随被遮罩的像素数的变化。该图显示出一小部分像素是造成大多数假击中的原因。不同的颜色对应于给定击中频率下的像素数目。只有几次击中的像素可以部分归因于宇宙线

图8 假命中率随被遮罩的像素数的变化。该图显示出一小部分像素是造成大多数假击中的原因。不同的颜色对应于给定击中频率下的像素数目。只有几次击中的像素可以部分归因于宇宙线

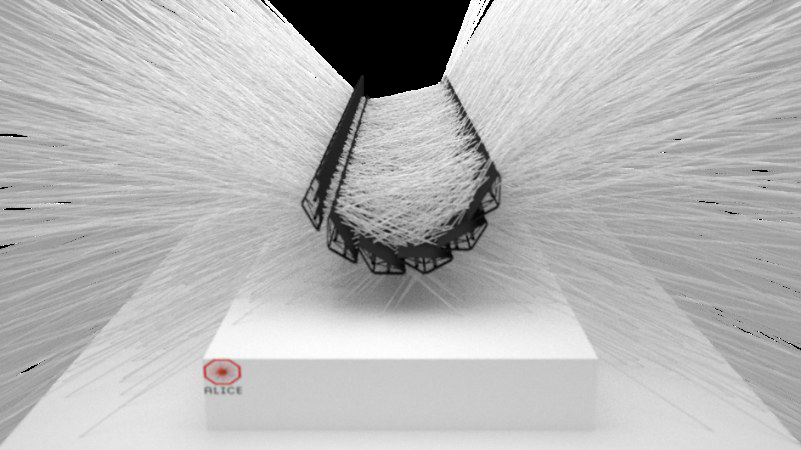

由于几何结构的重叠,一个单一的半层有一个小的、但不可忽略的重叠区,能使粒子穿越三个传感器,从而产生径迹上的三个点。基于此,可以重建出宇宙线的径迹。研究小组已经收集了大量的宇宙线样本(图9 显示了大约1400 个)。这些数据能用于验证事件读取和重建中的时间对齐,验证狭板的几何位置,并将依次(包括更多探测器层)用于ITS2的不同层之间所需的超精密空间位置校正。

图9 重建的第一批约1400 个宇宙线的三维视图

图9 重建的第一批约1400 个宇宙线的三维视图

06 结语

新的ITS 探测器是升级版ALICE 的一部分,在LHC的下一次运行中,它将提供一系列新的更精确的测量,以实现研究QCD和夸克-胶子等离子体特性的长期目标。

ITS2不仅将提高ALICE实验的物理性能,而且它的许多技术已经超越了国际上最先进的水平。目前,这项研发工作的成果不仅被应用于其他高能物理实验( 如BNL 的RHIC sPHENIX 和JINR 的NICA MPD实验的内寻迹系统),而且也被应用于其他领域。其中一个最热门的例子是,研发用于强子治疗癌症的质子计算机断层扫描(pCT)探测器。为ITS 升级而开发的ALPIDE芯片可以显著提高图像重建的精度,而同时能减少对患者辐照时间。

ALICE 合作组经过近10 年的巨大努力,成功研制出了ITS2 探测器,并将在今年内完成最终安装和调试,为2022 年投入LHC 第三期运行取数和发现新的物理现象铺平道路。

ALICE 中国团队(华中师范大学、中国原子能科学研究院、中国科技大学和复旦大学)在ITS2 研制过程中发挥了重要的作用。中方与ALICE 硅像素团队联合研发了国际上最先进的基于MAPS 技术的硅像素芯片,完成了450 个混合集成电路模块的集成与测试,在国内率先掌握了硅像素芯片设计和5 微米定位精度的芯片集成技术;并同期参与了基于MAPS硅像素芯片技术的ALICE 前向缪子径迹探测器的研制工作。通过国际合作,推动了国内自主研发新型TopMetal 芯片在兰州大科学实验装置束流检测中得到应用,以及将MAPS技术推广应用到我国CEPC 的硅像素顶点探测器的预研工作中,为国家重大科技战略服务。

图3 ALPIDE的图片(a)和读出结构(b)

图3 ALPIDE的图片(a)和读出结构(b)

图6 内筒的三个半层由24 个狭板组成。内筒将ITS2 的最内层固定在离束流管两毫米的位置

图6 内筒的三个半层由24 个狭板组成。内筒将ITS2 的最内层固定在离束流管两毫米的位置